西安电子科技大学 XIDIDIAN UNIVERSITY

V1.0 © 2007 韩孝勇 Han XiaoYong xyhan5151@yahoo.com.cn

集成电路设计流程及可靠性设计

# 4

## 本次课主要内容

IC设计流程及常用工具

基本概念

常用工具

可靠性设计技术简介

降额设计

冗余设计

灵敏度分析

最坏情况分析

可靠性模拟

## IC设计流程及常用工具

- 基本概念

- 全定制(Full -Custom)方式;

- 半定制 (Semi-Custom) 方式;

- 可编程逻辑器件(Programmable Logic Device, PLD)方式。

- Top- down

- bottom -up

- 正向设计

- 反向设计

### 各设计方法的优缺点

- 全定制方式是基于晶体管级的芯片设计,仔细考虑每个管子的尺寸、位置及管子间的互连关系,

- 缺点:比较慢,对设计人员要求高。作为一种改进,EDA工具提供标准单元库,库中有许多精心设计好的具有一定逻辑功能的标准单元。

- 半定制方式通常是指门阵列(Gate Array)方式。优点是用少量板,快

- 缺点是:由于基本单元之间保持固定的间距用于布线,必然存在某些地方走线稀疏(芯片面积利用率不高);而另一些地方走线拥挤,甚至连线布不通。 为了接通连线,还可能造成某些单元未被利用。

- 可编程逻辑器件是集成电路制造商向市场提供已封装完毕的芯片,其逻辑功能却可以由用户自己使用EDA工具"写入"。

- 可编程逻辑器件的缺点是:(1)芯片内部连线较长,速度相对较低。(2) 集成度相对较低。

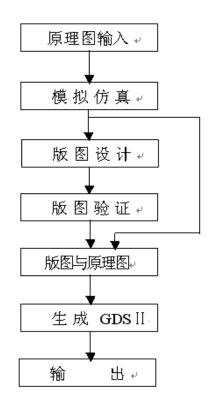

#### 全定制法设计流程

- 全定制通常利用人机交互图形系统,由版图设计人员人工地完成各器件及连线的版图设计、输入和编辑,实现电路图到版图的转换。

- 全定制版图设计的特点是充分利用设计人员的经验和创造力,尽可能对每个晶体管的电路参数与版图参数进行优化。

- 所以这种设计用于得到最高速度、 最低功耗和最省面积的芯片设计, 它的设计周期很长,设计成本很高。

图 全定制 IC 设计→

# 4

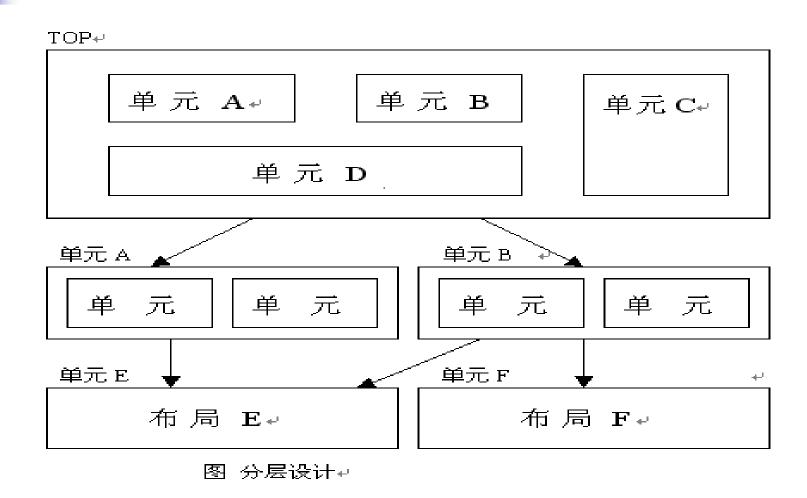

## 分层设计概念

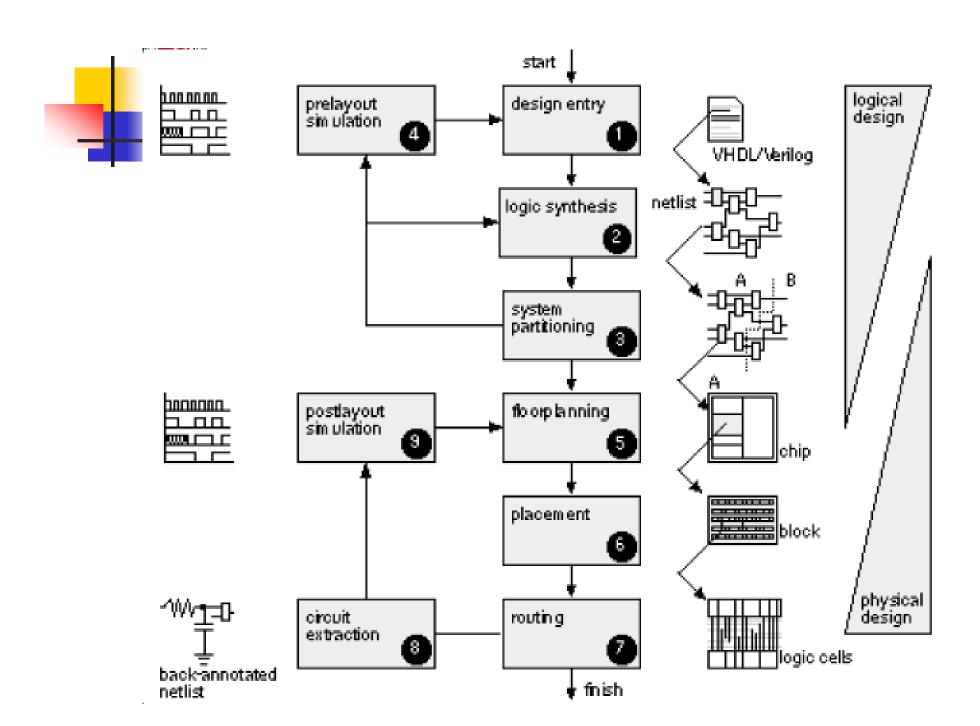

## 数字电路设计流程top-down

- 1. 设计输入

- 电路图或硬件描述语言

- 2. 逻辑综合

- 处理硬件描述语言,产生 电路网表

- 3. 系统划分

- 将电路分成大小合适的块

- 4. 功能仿真

- 5.布图规划

- 芯片上安排各宏模块的位置

- 6. 布局

- 安排宏模块中标准单元的 位置

- 7. 布线

- 宏模块与单元之间的连接

- 8. 寄生参数提取

- 提取连线的电阻、电容

- 9. 版图后仿真

- 检查考虑连线后功能和时序是否正确

# 反向设计

- 1、解剖

- 2、照相

- 3、提取

- 4、整理

- 5、逻辑仿真

- 6、版图(DRC,ERC, LVS)

- 7、PostSim

- 8、PG

- ❖ DRC:对 IC 版图做几何空间检查,以确保线路能够被特定加工工艺实现。

- ❖ERC:检查电源、地的短路,悬空器件和节点等电气特性。

- ❖LVS:将版图与电路原理图做对比,以检查电路的连接,与MOS的长宽值是否匹配。

- ❖LPE:从版图数据库提取电气参数(如MOS的W、L值BJT、二极管的面积,周长,结点寄生电容等)并以Hspice 网表方式表示电路。

#### •Diva

•Diva 是Cadence 的版图编辑大师Virtuoso集成的交互式版图验证工具,具有使用方便、操作快捷的特点,非常适合中小规模单元的版图验证。

#### •Dracula

- •Dracula(吸血鬼)是Cadence 的一个独立的版图验证工具,按 批处理方式工作,功能十分强大,目前是完整芯片验证的标准。

- •Diva和Dracula都可以做DRC LVS等

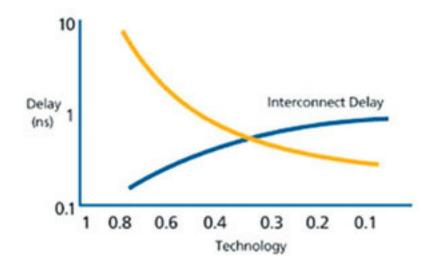

#### 从0.35微米工艺开始互连延迟已经开始大于门延迟

- 在近来的设计和验证会议(DVC2005) 上,已经指出,在5000万门设计中一 般需要700万行的RTL代码。这是对 人工设计一个巨大的挑战。

- 根据SIA在2000年发布的roadmap显示,2005年的最小特征尺寸已经到达80纳米,更将在2016年到达22纳米。

- 有研究结果显示,在1995年,集成电路的特征尺寸到达0.35微米的时候, 互连线时延已经占据了电路总时延的 50%,另外50%由电路门延迟占据。 当前,互连线延迟已经占据电路延迟的70%以上,这一现象还会更加严重。

#### Interconnect Delay vs. Gate Delay By Technology Generation

VHDL仿真 IKOS Vantage Cadence Synopsys Alta 行为综合 Synopsys Synopsys Compass Mentor Graphics 逻辑综合 Synopsys Sunrise 可测性设计 Compass 低功耗设计 Synopsys Epic Avant! **Mentor Graphics** 布局布线 Cadence Cadence Synopsys Compass IKOS Vantage 后仿真

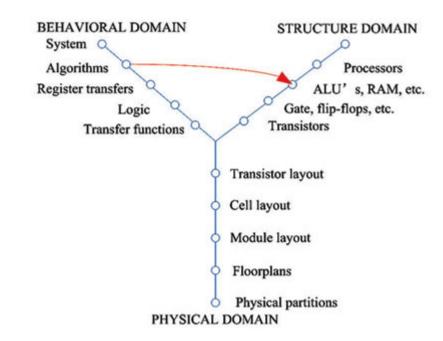

- 高层次综合在电路设计过程中的作用

- 在EDA设计流程中,高层次综合是连接系统行为和系统结构之间的纽带。

- 高层次综合在算法一级接受系统的行为描述,转换成为用功能单元、存储单元和互联元件(多路选择器,总线等)描述的电路结构。

# EDA工具

- 1、输入工具(design input):硬件描述语言(或是图形输入工具)图形输入工具

- 2、逻辑仿真工具(LOGIC SIMULICATION)

- 3、逻辑综合(logic synthesis)

- 4、自动布局布线(auto plane & route)系统;

- 5、物理规则检测(DRC & ERC)和参数提取(LVS)

- 除CADENCE公司以外,比较有名的公司包括mentor,avanti,synopsys和INVOEDA; mentor和cadence一样是一个在设计的各个层次都有开发工具的公司,而AVANTI因其模拟仿真工具HSPICE出名,SYNOPSYS则因为逻辑综合方面的成就而为市场认可。

## (1) 输入工具(design input)

- 对自顶而下的(TOP-DOWN)设计方法,往往首先使用VHDL或是 VERILOG HDL来完成器件的功能描述,代表性的语言输入工具有 SUMMIT公司的VISUAL HDL和MENTOR公司的RENIOR等。虽然很多的 厂家(多为FPGA厂商)都提供自己专用的硬件描述语言输入,如 ALTRA公司的AHDL,但所有的公司都提供了对作为IEEE标准的VHDL, VERILOGHDL的支持。

- 对自下而上(bottom-up)的设计,一般从晶体管或基本门的图形输入开始,这样的工具代表性的有cadence公司的composer;viewlogic公司的viewdraw等,均可根据不同的厂家库而生成和输入晶体管或门电路相对应的模拟网表。

### (2) 电路仿真软件(circuit simulation)

(分为数字和模拟两大类)

- 对于使用verilog HDL生成的网表,cadence公司的verilog-XL是基于 UNIX工作站最负盛名的仿真工具;

- 而近年随PC工作站的出现,viewlogic的VCS和mentor公司的modelsim 因其易用性而迅速崛起并成为基于廉价PC工作站的数字仿真工具;

- 对于VHDL网表仿真, cadence公司提供LEAFROG;

- SYNOPSYS公司有VSS,

- mentor公司基于PC的MODELSIM则愈来愈受到新手们的欢迎。

- PSPICE最早产生于Berkley大学,经历数十年的发展,随晶体管线宽的不断缩小,PSPICE也引入了更多的参数和更复杂的晶体管模型。使的他在亚微米和深亚微米工艺的今天依旧是模拟电路仿真的主要工具之一。

- AVANTI是IC设计自动化软件的"英雄少年",它的HSPICE因其在亚微 米和深亚微米工艺中的出色表现而在近年得到了广泛的应用。

- cadence公司的spectre也是模拟仿真软件,但应用远不及PSPICE和 HSPICE广泛;

## (3) 综合工具(synthesis tools)

- 用于FPGA和CPLD的综合工具包括有cadence的synplify;synopsys公司的FPGAexpress和FPGA compiler;mentor公司的leonardo spectrum; 一般而言不同的FPGA厂商提供了适用于自己的FPGA电路的专用仿真综合工具,比如altera公司的MAXPLUS2仅仅适用它自己的MAX系列芯片;而foundation则为XILINX器件量身定做......

- 最早的IC综合工具应该是cadence的buildgates;而Cadence最新版本的Envisia Ambit(R)则在99年在ASIC international公司成功用于240万门的设计。使用较广泛的还有synopsys的design compiler和behavial compiler;基于不同的库,逻辑综合工具可以将设计思想转化成对应一定工艺手段的门级电路;将初级仿真中所没有考虑的门沿(gates delay)反标到生成的门级网表中,返回电路仿真阶段进行再仿真。最终仿真结果生成的网表称为物理网表。

## (4) layout工具和自动布局布线 (auto plane & route) 工具

cadence的design framework是常用的基于UNIX工作站的全定制设计的布局布线软件,和silicon ensemble, Envisia place &route DSM; (cadence的版图输入工具Virtuoso)

## (5) 物理验证(physical validate)和参数提取(LVS) 可以分成为ASIC和FPGA两大类。

- ASIC设计中最有名、功能最强大的是cadence的DRECULA,可以一次完成版图从DRC(设计规则检查),ERC(电气特性检查)到LVS(寄生参数提取)的工序;DIVA作为其相对较弱的软件多提供给教学用途;

- AVANTI的STAR-RC也是用于物理验证的强力工具,而hercules则是其LVS的排头兵。

- 如同综合工具一样,FPGA厂商的物理验证和参数提取多采用专门的软件、并和其仿真综合工具集成在一起。ALTERA的MAXPLUS2和XILINX的FOUNDATION是这样的典型;

#### Synopsys公司EDA后端ASIC设计工具介绍

- Design\_Complier----对于这个工具大家并不陌生,它是一个综合工具,将前端设计好的verilog代码,综合成门级网表.

- Astro ------后端专门针对布线工具,将综合后的门级网表,吃进 Astro后,进行布局布线形成设计后端物理版图

- Jupiter-----是专门针对floorplan(布局)的工具,良好的布局是物理后端设计的关键,Jupiter就是专门针对布局的工具.

- Physical Compiler----专门针对place(摆放)的后端工具,摆放也是布局的一部分,是为route(布线)打好关键步骤的基础.

- Star\_RC -----后端寄生参数提取工具,将布局布线后的版图进行 参数提取,以便后面进行时序分

- Prime Time ----时序验证工具,参数提取后的RC进行计算setup time and hold time ,验证是否时序满足要求,如果时序不能满足要求,则要重新进行布局布线.

- Hercules -----DRC 和 LVS工具,按照工艺规则进行查错.

- 最后生成GDSII交付foundry流片

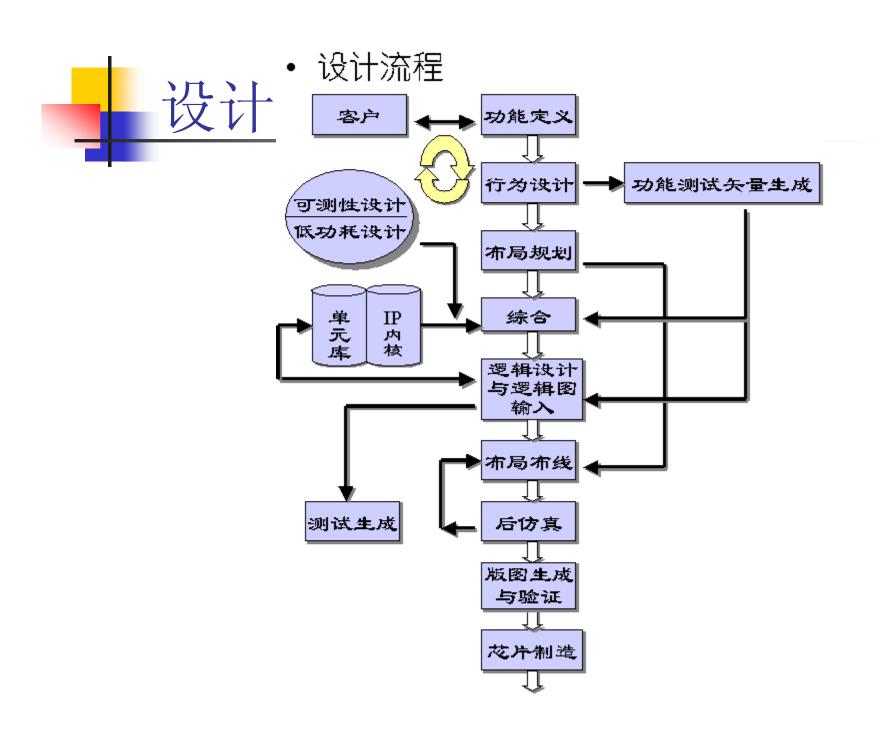

#### Candence常用的工具及全定制ASIC设计流程

- 1、用Candence原理图输入工具 composer进行原理图输入;生成 SCH文件,可以用EDIF格式导出;

- 2、用Candence数字仿真工具verilog-XL 或模拟仿真工具Anolog Artist(cdsspice spectre) 进行HDL 或原理图仿真;生成波形文件;

- 3、用Candence版图工具Virtuoso画版图; 生成layout版图文件;

- 4、画图过程中用Candence在线版图验 证工具DIVA进行DRC设计规则检查, 直到版图完成:

- 5、用Candence在线版图验证工具DIVA 进行ERC检查,并提取网表,待做 LVS:

- 6、用Candence在线版图验证工具 DIVA做LVS, 直到原理图与版 图对照完成;

- 7、用Copass或Candence模拟仿真 工具Anolog Artist(cdsspic spectre) 进行后仿真;

- 8、导出GDS格式版图文件;

- 9、用Candence版图验证工具 DRECULA再做DRC,ERC,LVS;

- 10、用Candence版图验证工具 DRECULA做PG处理;

- 11、交PG数据给制版商制版;

所有图片见文件icfb.doc

#### 没有EDA工具就没有IC

- 由于VLSI尤其是ULSI电路的预投片费用都相当的高(如TSMC 0.25um CMOS 工艺一次预投片的费用为100万美圆,而0.18um Cu CMOS 3.3V工艺的一次预投竟高达300万美圆)。因而对ASIC 芯片,要求芯片设计尽量正确。最好完全消灭错误;解决功耗分析;生成用于芯片测试目的的特殊测试电路;因应这一要求,也产生了一些特殊的EDA工具,以完成诸如power analysis、故障覆盖率分析、测试矢量生成等目的。

- 现代VLSI特别是ULSI IC的迅速发展, 正是依靠EDA工具在亚微 米和深亚微米技术上的进步及其对应工艺水平的提高。应该说没 有EDA工具就没有IC;

- 更没有高可靠性的IC;

## 可靠性设计的必要性

- 新需求和新问题对传统方法进行变革;

- 以前设计,制造,分析,改进

- 现在,失效率大为降低,可靠性试验很难做,新工 艺新问题

- 改变事后分析检测的方法,进行可靠性设计。

- 缩短投放市场的时间TTM:

- 以前3年一4年,大量时间化在产品层出不穷的问题的解决上。

- 现在,TTM已逐步缩短为6个月(一次投片成功)

## 微电路可靠性设计的特点

- 整机可靠性设计是以失效率指标为对象.进行可靠性分配、设计、预计的。而微电路可靠性设计则是以失效模式为对象,围绕如何控制或消除这些失效模式设计工作的。

- 整机和系统的可靠性设计已有几十年的发展历史,理论体系比较成熟,并有一套定量的设计计算方法。而对微电子器件仅有十几年,目前尚未形成比较全面、系统的理论体系。

- 微电路中目前采用的可靠性设计技术大多是定性范畴。

- 需进行定量分析计算的工作有两类;一类是直接引用整机和系统中的设计技术,如降颜设计、灵敏度分析等:另一类是微电路的可靠性模拟。

## 常规可靠性设计技术

- 降额设计

- 冗余设计

- 灵敏度分析

- 最坏情况分析

## 降额设计

- ■基本原理

- 微电路中由主要失效机理决定的平均寿命可统一 表示为公式:

#### $t_{MTTF} \sim F^{-m}.exp(Ea/KT)$

- F为作用应力(如电流密度,电场强度等),m为常数指数,T为工作温度,Ea为激活能;

- 由上式知:激活能确定时,要提高可靠性,就应 该降低应力强度。

## 降额设计应注意的问题

- 能降则降,不能降则不降。比如电压降低,引起阈 值电压噪声等其他问题时不降。

- 降额引起的其他问题

- 版图面积,关键部分进行降额设计。

## 冗余设计

- 基本概念:

- 有单元失效时,不应影响系统的正常工作。

- 热储备

- 连接单元同时在工作。

- ▶冷储备

- 连接单元不工作,需要时才启动。

## 静态冗余和动态冗余

- ■静态冗余

- 单元数多于需要的数目,在最后连现时进行舍去 一些不好的单元。

- 动态冗余

- 热储备和冷储备

## 灵敏度分析

- 含义

- 定量分析电路对不同元件标称值变化的影响,找出 对电路影响最大的元件。

- 定量表示

- (元件)绝对灵敏度和相对灵敏度

- 应用

- ■做仿真用

## 最坏情况分析

#### ■ 概念

■ 按电路特性向同一方向变化时的要求,确定每个元件的变化 方向,在使这些元件同时变化进行分析(最坏情况下)

#### ▶ 步骤

- 先进性标称值分析;

- 在进行灵敏度分析,确定元件变化方向

- 确定最坏方向;

- 按最坏方向进行分析。

#### 应用

■ 了解最坏情况会如何(一般不会遇到),所以正常使用更应该没有问题。

## 可靠性模拟

- 概念

- 区别于逻辑仿真/后仿真

- ■技术问题

- 建立模型,提取模型参数

- 版图数据处理,提取版图参数结点电应力

- 计算单一模式的可靠性,再综合。

## 可靠性模拟

- 应用

- 预计可靠性水平

- 发现薄弱环节

- ■协调电参数和可靠性的关系

- 现状和发展方向

- 只能模拟中小规模的电路。BERT程序

- 现在只在管子级

- 针对单一失效机理模拟

# 内建可靠性

- 1、 考虑问题的出发点从失效率转为失效机理

- 2、 对失效机理的分析重点从输出转向输入

- 3、 对工艺问题将从被动检测工艺结果变为主动控制工艺变量

- 4、 控制工艺输入变量的理想目标是无偏差,无缺陷

- 5、 内建可靠性是综合技术

- 可靠性的表征:从普通可靠性指标改为SPC参数 PPM 技术 6西格玛技术等(明白牌子的重要)

# 本次课小结

- ■设计流程

- ■基本概念

- ■常用工具

- 为什么要进行可靠性设计? 常用方法